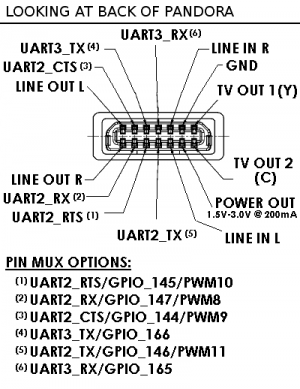

EXT Connector

Contents

What does it have?

- UART2

- UART3

- TV out

- Stereo line out

- Stereo line in

- The UART lines can also be used as GPIO (six of them) and PWM lines (four of them).

Note that Power Out defaults to 2.8V, while the digital I/O lines work with 1.8V logic. To avoid damaging the Pandora, a level shifter will be required for most applications using these signals.

Connectors

Just for reference: the Pandora-side of the connector is Tyco 1717312-1, you already have that. [1]

Astron Connector

- Astron, part number 3111014-301-R

- Available from DragonBox for 7 EUR each [2]

Tyco Connector

- Tyco Electronics, part number 1717169-2 [3]

- The manufacturer does *not* stock these for engineering samples, and very few vendors carry them

- Community member WizardStan ordered a bunch and sold them for $2 each plus shipping from Canada [4]

- Community members peca and Nardella designed and manufactured a break-out-board for easier soldering [5]

How Do I Make a TV-Out Cable?

- There are some useful tips in the EXT Connectors thread.

- A guide explaining one way of creating the video cables can be found here

- MarkoeZ Has written a blog post about it here

Pin functions (mux)

By default the UART2 pins are set up as GPIOs, and UART3 is set up as an UART. The following describes how to change pin functions under a 3.2 kernel.

Setup

As root,

mkdir /debug

mount -t debugfs none /debug

In the /debug/omap_mux directory which appears, the files relevant to the EXT connector are uart2_cts, uart2_rts, uart2_rx, uart2_tx, uart3_rx_irrx, uart3_tx_irtx. They are mapped to the pad configuration registers. Reading one of these files reports the current configuration of the pin. Writing the appropriate pattern to the file changes the configuration of the pin.

Pad Configuration Register

As described in OMAP35x Technical Reference Manual (Rev. Y), section 7.4.4 [6]

| Bits | Name | Comments |

|---|---|---|

| 15 | WAKEUPEVENT | |

| 14 | WAKEUPENABLE | |

| 13 | OFFPULLTYPESELECT | |

| 12 | OFFPULLUDENABLE | |

| 11 | OFFOUTVALUE | |

| 10 | OFFOUTENABLE | |

| 9 | OFFENABLE | |

| 8 | INPUTENABLE | 0: output only. 1: bidirectional. |

| 7,6,5 | RESERVED | |

| 4 | PULLTYPESELECT | 0: pull-down. 1: pull-up. |

| 3 | PULLUDENABLE | 0: pull not active. 1: pull active when pin direction is configured as input. |

| 2,1,0 | MUXMODE | See table below. |

Mux modes

| Mode 0 | Mode 1 | Mode 2 | Mode 3 | Mode 4 | Mode 5 | Mode 6 | Mode 7 |

|---|---|---|---|---|---|---|---|

| uart2_cts | mcbsp3_dx | gpt9_pwm_evt | NA | gpio_144 | NA | NA | safe_mode |

| uart2_rts | mcbsp3_dr | gpt10_pwm_evt | NA | gpio_145 | NA | NA | safe_mode |

| uart2_tx | mcbsp3_clkx | gpt11_pwm_evt | NA | gpio_146 | NA | NA | safe_mode |

| uart2_rx | mcbsp3_fsx | gpt8_pwm_evt | NA | gpio_147 | NA | NA | safe_mode |

| uart3_rx_irrx | NA | NA | NA | gpio_165 | NA | NA | safe_mode |

| uart3_tx_irtx | NA | NA | NA | gpio_166 | NA | NA | safe_mode |

Example

Example of changing UART2_RTS from GPIO to UART mode [7]:

# cat /debug/omap_mux/uart2_rts

name: uart2_rts.gpio_145 (0x48002176/0x146 = 0x010c), b ab25, t NA

mode: OMAP_PIN_INPUT_PULLDOWN | OMAP_MUX_MODE4

signals: uart2_rts | mcbsp3_dr | gpt10_pwm_evt | NA | gpio_145 | NA | NA | safe_mode

# echo 0x0108 > /debug/omap_mux/uart2_rts

# cat /debug/omap_mux/uart2_rts

name: uart2_rts.uart2_rts (0x48002176/0x146 = 0x0108), b ab25, t NA

mode: OMAP_PIN_INPUT_PULLDOWN | OMAP_MUX_MODE0

signals: uart2_rts | mcbsp3_dr | gpt10_pwm_evt | NA | gpio_145 | NA | NA | safe_mode

The value was changed from 0x010c to 0x0108. In both numbers, bit8 is 1 for input enable, bit4 is 0 for pull-down, and bit3 is 1 for pull enable. Bits 2,1,0 changed from 4 to 0, which changed the mux mode from 4 to 0.

Power supply

Currently always set to supply 2.8V, changing this requires patching bootloaders (xload and u-boot).

This is connected to VAUX3 supply on PMIC, with these programmable voltages (200mA max): 1.5V, 1.8V, 2.5V, 2.8V and 3.0V, with 2.8V as default.

Warning: at the time of this writing, both bootloaders (xload and u-boot) set this to 2.8V unconditionally, so don't rely on this providing other voltages during reboot until you patch both bootloaders. The digital I/O pins use 1.8V logic and must not be connected to the 2.8V from the power pin!

GPIOs

Can be controlled using GPIO sysfs class device, as described in beagleboard tutorials here.

The pins must be set as GPIO using the pin mux.

In the following commands, NNN is the GPIO number, e.g. 145.

#enable gpioNNN folder, to prepare for the other commands

echo NNN > /sys/class/gpio/export

#reads "in" or "out" depending on what was written to it

cat /sys/class/gpio/gpioNNN/direction

#when direction is "out", reads 0 or 1 depending on what was written to it

#when pinmux specifies bidirectional and direction is "in", reads 0 or 1 depending on voltage at pin

#when pinmux specifies output-only and direction is "in", always reads 0

cat /sys/class/gpio/gpioNNN/value

#set value to 0, i.e. output low (only works when direction is "out")

echo 0 > /sys/class/gpio/gpioNNN/value

#set value to 1, i.e. output high (only works when direction is "out")

echo 1 > /sys/class/gpio/gpioNNN/value

#set direction to "in"

echo in > /sys/class/gpio/gpioNNN/direction

#set direction to "out" and value to 0, i.e. output low

echo out > /sys/class/gpio/gpioNNN/direction

#set direction to "out" and value to 1, i.e. output high

echo high > /sys/class/gpio/gpioNNN/direction

#set direction to "out" and value to 0, i.e. output low

echo low > /sys/class/gpio/gpioNNN/direction

#disable gpioNNN folder

echo NNN > /sys/class/gpio/unexport

Controlling the GPIOs with shell script like this is very slow; if speed is required, choose another language to write to the files more efficiently.

UART

UART2 is mapped to /dev/ttyO1 and UART3 is mapped to /dev/ttyO2.

The line is high when idle. Each item transmitted has a start bit (low); 5, 6, 7 or 8 data bits; an optional odd or even parity bit; and 1 or 2 stop bits (high).

These UARTs support a wide range of baud rates. UART2 has the RTS and CTS pins brought out to the EXT connector, while UART3 does not.

See the Serial Programming Guide for POSIX Operating Systems.

PySerial works for configuring and using the ports.

UART3

On older firmwares, kernel messages are directed there. SuperZaxxon or later have that disabled.

On all firmwares released so far terminal with a shell is attached to UART3. The port runs at 115200 8N1 baud rate.

Disabling kernel messages

To disable kernel mesages, you need to edit kernel boot arguments. Probably easiest way to do it is to create autoboot.txt and place on root directory of a card in slot1 with this content:

setenv bootargs ubi.mtd=4 ubi.mtd=3 root=ubi0:rootfs rootfstype=ubifs rw rootflags=bulk_read

Alternatives are using u-boot environment (configure through USB or UART3 serial before system boots up) or patching and reflashing u-boot itself.

Disabling attached terminal

For this you need to edit /etc/inittab on pandora rootfs and comment out these lines:

#S0:2345:once:/sbin/getty 115200 ttyS0

#O2:2345:once:/sbin/getty 115200 ttyO2

PWM

The UART2 pins on the OMAP could be configured for PWM, but there does not seem to be an interface in the Pandora's OS to do this.

A wide variety of PWM output can be improvised with a UART. The start bit is always low and the stop bit(s) are always high, but the other bits depend on the character sent and the parity selection. The number of bits per character can be changed between 7 and 12, giving several options for frequency division within each available baud rate.

_^_^_^_^_^ 8 data bits; frequency=baudrate/2; duty cycle 50%

_^^^^^^ 5 data bits; frequency=baudrate/7; duty cycle 6/7

__________^^ 8 data bits, even parity and 2 stop bits; frequency=baudrate/12; duty cycle 1/6